有奖调查:达尔闻即将要推出一套TI的权威电源培训系列课程,线上培训+线下EVM实操。在此之前,我们设定了一些问题,希望了解大家的需求,我们会送出一些精美礼品。

今天继续为大家解析艾为电子数字IC设计岗剩下的笔试题。

4、程序改错题(10分)

//-----------------------------

01moduletest(

02inputclk,

03input[7:0]addr,

04inputreq,

05inputrst_n,

06inputwen,

07input[15:0]wdata,

08output[15:0]datao,

09)

10

11reg[15:0]mem[7:0];

12

13always@(posedgeclkornegedgerst_n)begin

14if(rst_n)begin

15mem=0;

16elseif(wen)begin

17mem[addr]=wdata;

18

19

20always@(req)

21if(req)

22datao=mem[addr];

23

24module

//----------------------------

解析:本题主要考察了对Verilog语法规范的敏感性。这种题目在没有编译器的情况下,纯靠观察来找语法问题,需要对Verilog代码有一定的敏感度才能够找全。如果是一个新手或者写代码不多的人想在短时间内全部把错误都找出来还是有些困难的。根据分值设置和代码量可以初步预判大概有不少于5个的错误。错误如下所示:

1)第08行的结尾,不能有“,”

2)第09行的结尾,应该有“;”

3)第16行的“begin”没有与之匹配的“”

4)第15行二维数组在赋初值时不能直接分配给数组整体初值,只能分配给单个元素初值,也可以使用initial读取初始化文件中的初始化值

5)datao信号在always块中被赋值,所以第08行应该把datao信号定义为reg型变量,缺省情况下默认为wire型变量

另外还有两处不严谨的地方,这种不严谨的问题虽然在本次设计中不会出现问题,但是并不推荐这种写法,具有潜在的危险:

1)第一个表达时序逻辑的always块应该推荐使用“=”赋值方式,第二个表达组合逻辑的always块应该推荐使用“=”赋值方式

2)第20行always块中的敏感列表不全,推荐使用通配符“*”

还有一处需要注意的地方:在表达组合逻辑的第二个always块中的“if”没有对应的“else”,这虽然不能算是错误,但产生latch时一定要是设计者已知的。

修改完毕后的代码如下所示:

//------------------------------

01moduletest(

02inputclk,

03input[7:0]addr,

04inputreq,

05inputrst_n,

06inputwen,

07input[15:0]wdata,

08outputreg[15:0]datao

09);

10

11reg[15:0]mem[7:0];

12

13always@(posedgeclkornegedgerst_n)begin

14if(rst_n)begin

15mem[addr]=15'd0;

16elseif(wen)begin

17mem[addr]=wdata;

18

19

20

21always@(*)

22if(req)

23datao=mem[addr];

24else

25datao=15'd0;

26

27module

//---------------------------------

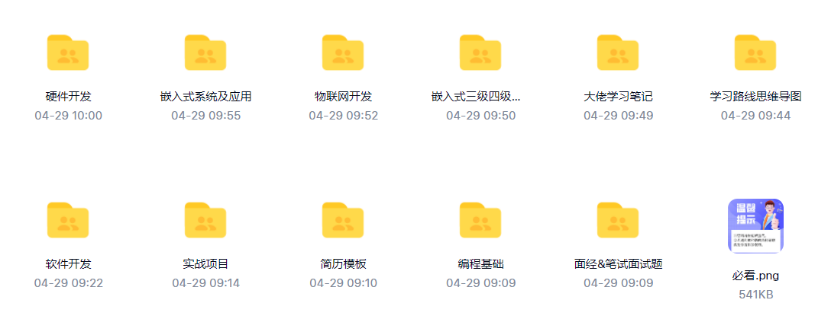

嵌入式物联网需要学的东西真的非常多,千万不要学错了路线和内容,导致工资要不上去!

无偿分享大家一个资料包,差不多150多G。里面学习内容、面经、项目都比较新也比较全!某鱼上买估计至少要好几十。

5、用Verilog实现串转并电路,输出信号8bit,同时可选择模式LSB或者MSB优先。(10分)

解析:本题主要考察了可切换的串并转换的Verilog实现

串并转换在Verilog中经常会用到,由于芯片外部的PAD数量有限,所以多用串行的方式把数据送入,然后在芯片内部再转成并行数据进行处理。我们可以选择用寄存器移位的方式实现,也可以选择用FIFO或RAM来实现,这题显然是要求我们用寄存器移位的方式来实现。题目中还要求LSB和MSB可切换的功能,这里我们通过一个输入信号来控制,这个信号在芯片中往往都是做成寄存器可配,由专门的regbank模块来控制。Verilog代码如下所示:

//------------------------------

01moduleserial2parrallel(

02inputsys_clk,//模块的时钟

03inputsys_rst_n,//模块的复位

04inputreg_msb_lsb,//为1时表示先传来的MSB数据,为0时表示先传来的LSB数据

05inputdata_in,//单比特串行数据

06inputdata_in_valid,//单比特串行数据有效标志信号

07

08outputreg[7:0]data_out,//8比特串并数据

09outputregdata_out_valid//8比特串行数据有效标志信号

10);

11

12reg[2:0]cnt;

13

14//当单比特串行数据有效标志信号有效时计数器计数

15always@(posedgesys_clkornegedgesys_rst_n)

16if(!sys_rst_n)

17cnt=3'b0;

18elseif(data_in_valid==1'b0cnt==3'd7)

19cnt=3'b0;

20elseif(data_in_valid==1'b1)

21cnt=cnt+1'b1;

22

23//当单比特串行数据有效标志信号有效且先传来MSB数据执行左移;当单比特串行数据有效标志信号有效且先传来LSB数据执行右移

24always@(posedgesys_clkornegedgesys_rst_n)

25if(!sys_rst_n)

26data_out=8'b0;

27elseif(data_in_valid==1'b1reg_msb_lsb==1'b1)

28data_out={data_out[6:0],data_in};

29elseif(data_in_valid==1'b1reg_msb_lsb==1'b0)

30data_out={data_in,data_out[7:1]};

31

32//当移动8次后,8比特并行数据有效

33always@(posedgesys_clkornegedgesys_rst_n)

34if(!sys_rst_n)

35data_out_valid=8'b0;

36elseif(cnt==3'd7)

37data_out_valid=1'b1;

38else

39data_out_valid=1'b0;

40

41module

//---------------------------------

Testbench如下所示:

//---------------------------------

01`timescale1ns/1ns

02

03moduletb_serial2parrallel();

04

05regsys_clk;

06regsys_rst_n;

07regreg_msb_lsb;

08regdata_in;

09regdata_in_valid;

10

11wire[7:0]data_out;

12wiredata_out_valid;

13

14//初始化系统时钟、全局复位和输入信号

15initialbegin

16sys_clk=1'b1;

17sys_rst_n=1'b0;

18reg_msb_lsb=1'b1;

19data_in=1'b0;

20data_in_valid=1'b0;

21200

28data_in_byte();

29

30

31//sys_clk:每10ns电平翻转一次,产生一个50MHz的时钟信号

32always(20);//没间隔20ns发送1比特数据

61

62task

63

64//--------serial2parrallel_inst------

65serial2parrallelserial2parrallel_inst(

66.sys_clk(sys_clk),//inputsys_clk

67.sys_rst_n(sys_rst_n),//inputsys_rst_n

68.reg_msb_lsb(reg_msb_lsb),//inputreg_msb_lsb

69.data_in(data_in),//inputdata_in

70.data_in_valid(data_in_valid),//inputdata_in_valid

71

72.data_out(data_out),//output[7:0]data_out

73.data_out_valid(data_out_valid)//outputdata_out_valid

74);

75

76module

//-------------------------------

仿真结果这里不再给出,大家可以自行验证一下。

6、艾师傅卖羊肉,进价24一公斤,卖18一斤,客人买了四公斤,客人给两百元但找不开,艾师傅到邻居家换了两百元钱,后来邻居去银行存钱发现这两百元是假币,艾师傅又赔了邻居200,请问艾师傅一共赔了多少钱?(10分)

解析:本题主要考察了如何从复杂的逻辑中理清关键逻辑

卖4公斤肉亏的钱就是进肉价格所亏的本钱为:24¥/kg*4kg=96¥;200元假币找零所亏的钱为:200¥-36¥/kg*4kg=56¥,所以艾师傅总的亏损为:96¥+56¥=152¥。

文章链接:

转载自:达尔闻说,作者相量子

文章链接:求职攻略|如何用Verilog实现串转并电路